This represents the FPGA on the Digilent board providing access to the various IO.

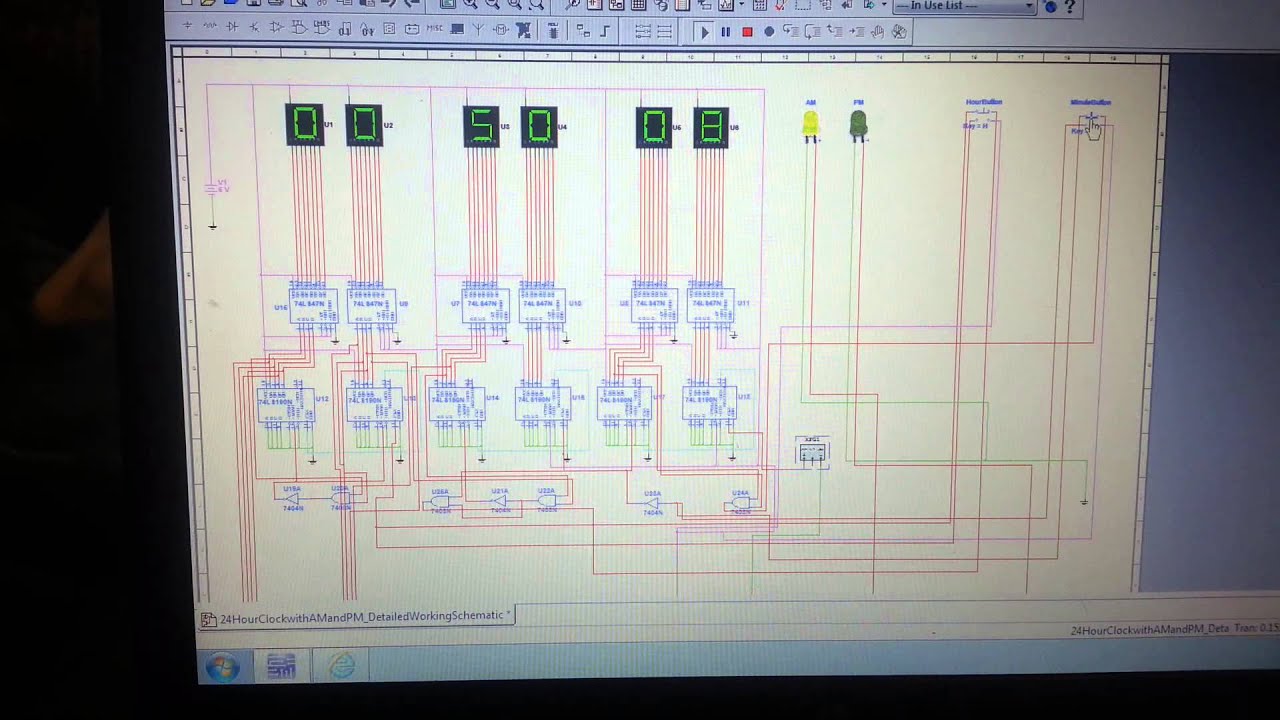

Whilst this tutorial and the accompanying example were produced using the Digilent Nexys 3 the same could be achieved on other Digilent boards. This tutorial is going to provide an example of how students can develop counters using Digilent boards and use these to control the onboard 7 segment displays. Using Multisim and the PLD schematic students can gain experience of using counters in hardware before the need to learn these more advanced descriptive languages. Typically, using traditional approaches this would require the student to learn advance Hardware Descriptive Languages such as VHDL and Verilog. Gaining a comprehension of timing is difficult without using hardware because of the inability for software based simulations to meet the speed of those running in hardware. When moving beyond simple logic diagrams, timing soon becomes a critical part of digital design.

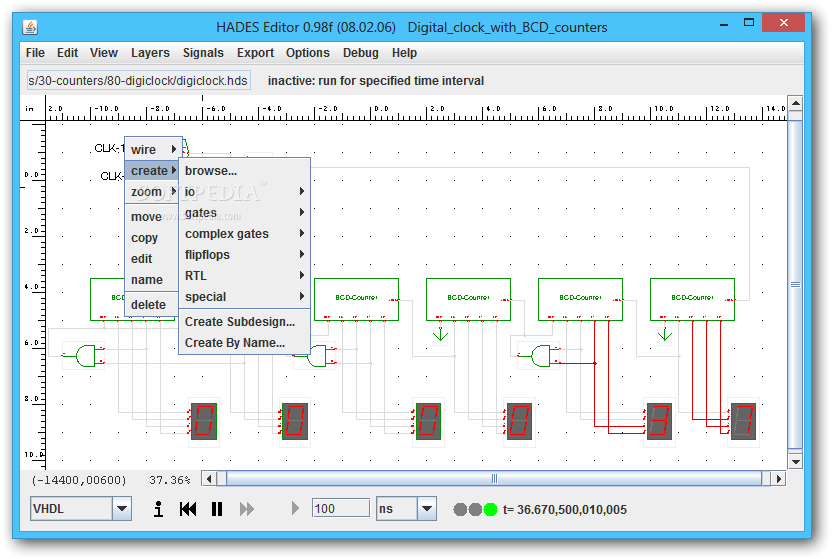

View the complete Teaching Digital Logic Fundamentals tutorial series. In this set of tutorials we demonstrate how digital logic theory can be taught using educational hardware to provide a hands-on approach to learning. The PLD schematic allows educators and students to create graphical logic diagrams like those found in textbooks and deploy these to Digilent educational boards. Multisim Programmable Logic Diagram (PLD) along with support for leading Digilent teaching hardware allows students to put the fundamentals of digital theory into practice. Taking a hands-on approach to learning digital logic can be difficult without the need for students to learn complex hardware descriptive languages (eg.

0 kommentar(er)

0 kommentar(er)